Vortex AT-ONCE remake project

W jakiś przedziwny sposób rozpoczęła się nowa przygoda z kolejnym emulatorem.

Zmontowałem dla Marcina

klon PC-Speed i tak - przy okazji - dowiedziałem się, że jest

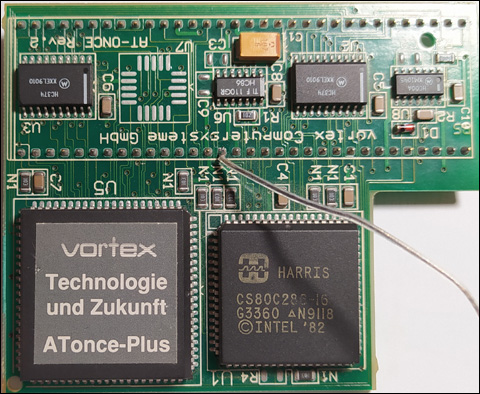

on posiadaczem oryginalnego emulatora AT-ONCE PLUS produkowanego przez firmę

Vortex Computersysteme GmbH w latach 90 poprzedniego stulecia :) Jako, że nigdy

nie widziałem żeby ktokolwiek odkleił nalepkę firmową z układu Gate Array - poprosiłem

Marcina o to czy mógłby to zrobić.

I on to zrobił!! Zdjął nalepkę z układu PLCC84,

a pod nią ukazało się to: Widok poszlifowanego układu w AT-ONCE Marcina:

No i weź tu cokolwiek wykombinuj. Teraz wiem, dlaczego przez tyle lat nikt nawet

chyba nie usiłował odtworzyć emulatora. Po pierwsze żal odklejać oryginalną nalepkę,

po drugie - starte oznaczenia układu scalonego pod nalepką. Samo życie...

Jednak przyglądając się dłużej tym resztkom farby na obudowie scalaka zacząłem

zauważać coś bardzo ciekawego. Jako, że najczęściej pracuję z układami firmy Xilinx,

pozostawione ślady szybko ujawniły mi wzór nadruku firmowego. Trafiony w 100%.

Przez jakiś czas próbowałem dopasować zdjęcia i wzory. Efekt poniżej:

(obrazek poglądowy zrobiony już po odnalezieniu właściwego typu FPGA)

Wiedziony ciekawością rozpocząłem poszukiwania. Najpierw znalazłem katalogi

produktów Xilinx z roku 1989 na bitsavers.org i sprawdziłem, które układy mają wersje

w obudowach PLCC84 - niestety - okazało się, że prawie wszystkie ;-) W międzyczasie

okazało się, że kolega z forum Atari Area Atari-User posiada dokładnie taki sam

emulator i może dla mnie sprawdzic kilka rzeczy miernikiem. Chodziło mi najpierw o

sprawdzenie do których nóżek układu scalonego jest doprowadzone zasilanie. Po

sprawdzeniu przez niego połączeń i porównaniu z danymi katalogowymi, wybór układów

dramatycznie się zawęził. Odpadły CPLD z rodziny XC9500 oraz FPGA z rodziny

XC4000. Pozostały do ogarnięcia układy rodzin XC2000 oraz XC3000. Poprosiłem

Atari-Usera o wypożyczenie emulatora do przeprowadzenia głębszej nieniszczącej

analizy oraz odtworzenia schematu co zrobiłem dosyć szybko, lecz niestety z jednym

krytycznym błędem. Później wypożyczyłem układ jeszcze raz, zweryfikowałem całość

dwukrotnie i obecnie jest to 100% dokładny schemat emulatora.

Tak wygląda część mojego "warsztatu" reverse engineer

Odtworzony i sprawdzony schemat w pdf

`

oraz Eagle AT-ONCE Eagle schematic file Pliki w formatach Gerber oraz Excellon

AT-ONCE Gerber and Excellon files

Dzięki użytkownikowi z forum Atari-Forum - Adrianowi otrzymałem możliwość

zamieszczenia tu instrukcji montażu oraz obsługi AT-once Plus w języku niemieckim

Wielkie podziękowania dla niego oraz dla człowieka, który zeskanował dokument.

Brak jest stron 8 i 9, ale to nie powinno zbyt przeszkodzić w korzystaniu. User manual/ installation manual AT-once Plus (GER)

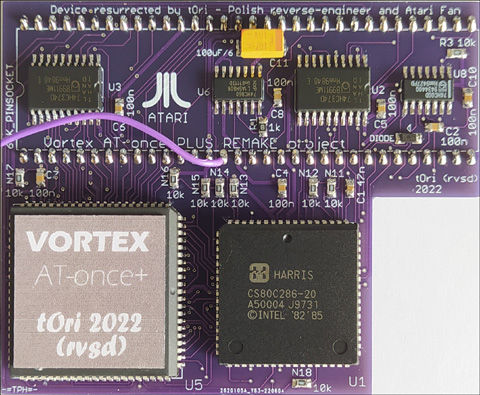

Projekt PCB jest dwuwarstwowy, wykonanie w warunkach amatorskich raczej nie jest

zbyt możliwe ze względu na wiele wąskich ścieżek. Osobiście zamawiam PCB w

Chinach. Dokładniej zaś w JLCPCB. Szybko, względnie tanio i przede wszystkim -

dobrze. Polecam :)

Bardzo proszę u nieusuwanie z PCB napisu tOri - dziękuję Szybko okazało się, że znalezienie właściwego układu FPGA będzie dosyć trudne.

Na szczęście znalazłem dobre źródło tanich, używanych układów XC3020, XC3030 oraz

XC3042, bo wydawalo mi się, że został zastosowany któryś z układów tej rodziny.

Układy XC3064 oraz XC3090 odpadły ze względu na różnice w doprowadzeniu zasilania.

Po dotarciu zamówionych PCB z Chin złożyłem jedną sztukę z układem XC3042.

Niestety - emulator nie zadziałał... Zmontowałem więc kolejną sztukę tym razem z

podstawką pod układ FPGA i pomimo przekładania różnych układów - nie działało!

Atari zawisał przy włączeniu zasilania tak, jakby coś mu na szynach zawadzało :/

Metodą prób i błędów znalazłem problem dotykający linię danych D1. Po wyizolowaniu

tej linii od strony emulatora komputer sie uruchomił. Dalsze poszukiwania skierowały

mnie w stronę rodziny XC2000 i w niej tylko jeden układ - XC2018 wydawał się spełniać

warunki wynikające ze schematu połączeń. Tak więc poszukiwanym FPGA ostatecznie okazał się: XC2018

Po zmontowaniu kolejnej sztuki z poprawionymi połączeniami oraz układem 2018

emulator zadziałał od razu.

Kilka uwag związanych z konstrukcją. Procesor 80286 powinien mieć minimalną

częstotliwość pracy 16MHz. XC2018 może być z dowolną prędkością. I tak minimum

dla niego to 50MHz. Pozostałe elementy według schematu. Zegar 16MHz jest brany

z nóżki 39 układu SHIFTER poprzez dolutowanie kabelka z nóżki 15 emulatora.

Projekt PCB umożliwia zamontowanie na padach SMD podstawek pod FPGA

oraz CPU. Tak wygląda zainstalowany emulator w moim komputerze Mega4

Ekran startowy AT-ONCE:

SOFTWARE AT-ONCE (click!) Proszę użyć pliki z katalogu ATONCE_P.LUS

Finalna wersja emulatora Vortex AT-once Plus

UAKTUALNIENIE:

Dzięki imponującej pracy wykonanej przez Zippy'ego (of Medway Boys) poznanego

przeze mnie na forum Atari-Forum.com zamieszczam wyodrębnione dane dla FPGA

XC2018 zastosowanej w AT-ONCE.

Kilka istotnych uwag

- jako, że konstrukcja oraz format danych są chronione przez

XilinX - odtworzenie układu połączeń jest poważnym wyzwaniem i choć jest niezwykle

trudne to, jak twierdzi ijor

(sprzętowiec z AF), jest zadaniem wykonalnym. Być może

tak, a może nie :) Dla każdego chętnego pliki są dostępne do analizy. Jak napisał

Zippy

- dane zawarte w tablicy LOGBYTEB.BIN to dane przeznaczone dla AT-ONCE

PLUS - czyli wersji 2 emulatora taktowanej 16MHz. W archiwum jest kilka plików,

gdzie: ATONCE.BIN i ATONCE1.BIN wydają się być systemem BIOS emulatora PC,

a pliki LOGBYTE oraz LOGBIT są strumieniami bitów przedstawionymi w konwencjach

bajtowej i bitowej. Długość strumienia bitów wynosi 17888 bitów i jest dłuższa od

standardowej długości określonej w datasheet XC2018 o 10. Z pewnością jest jakiś

powód za tym stojący, choćby dummy bits, których ilość jest określona w dokumencie

jako minimalna (4 bity - 1111 - minimum) dotyczy to zarówno pre- i postambuły.

Dla chętnych zamieszczam niezbędne oraz pomocne pliki:extracted files package from Zippy -

ATONCE Bitstreams.ZIP

XC2000 Family datasheet

Ken Schriff's reverse-engineering the first FPGA chip (www)

Methods of Reverse Engineering a Bitstream for FPGA protection article

Przekazuję wszystko za darmo dla świata użytkowników Atari. Taka idea leży u

podstawy moich działań na scenie. Dopóki będę miał możliwośći - odtworzę to co się

nadaje do odtworzenia. Już i tak nauczyłem się mnóstwa ciekawych tricków. Pora

więc na kolejne...

Proszę o uszanowanie mojego czasu i wysiłku

włożonych w reversing AT-ONCE.

Wykorzystanie komercyjne zamieszczonych materiałów jest ZABRONIONE i to nie zostanie przeze mnie zmienione. |