# Constructional Project

# DIGITAL I.C. TESTER

### JOE FARR

Let a PIC and a PC check the health of your digital logic chips.

URING project construction, many hobbyists must have wondered if the reason their masterpiece wasn't working was due to a faulty i.c., or if the i.c. they've just removed from an old board actually works. The project described here provides a simple way to quickly test the operation of most TTL and CMOS digital

#### **HOW IT WORKS**

To explain how the Digital I.C. Tester works, let's examine the humble 7400 TTL NAND gate device as an example. The datasheet says the package contains four logic gates, each one having two inputs and one output, which behave according to the truth table in Table 1.

Table 1. Truth table for a 2-input NAND gate

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| L       | L       | Н      |

| L       | Н       | Н      |

| Н       | L       | Н      |

| Н       | Н       | L      |

To test the satisfactory functioning of each of the four gates in the i.c. package, each of the four input logic configurations in Table 1 must be applied to each gate and the resulting logic output levels recorded and compared against the expected results.

A profile for an i.c. to be tested is first generated from the device's datasheet. Within the profile, an instruction sequence is specified that applies defined logic levels to the specified input pins, and records the results generated on the output pins.

The actual results received are compared against those that are expected, and from this it is possible to ascertain if the i.c. is functioning correctly.

It should be noted that some i.c.s require a great many individual logic operations to test them completely. For example, the 7430 8-input NAND gate requires 256 separate input logic level permutations to be tested

#### **CIRCUIT DESCRIPTION**

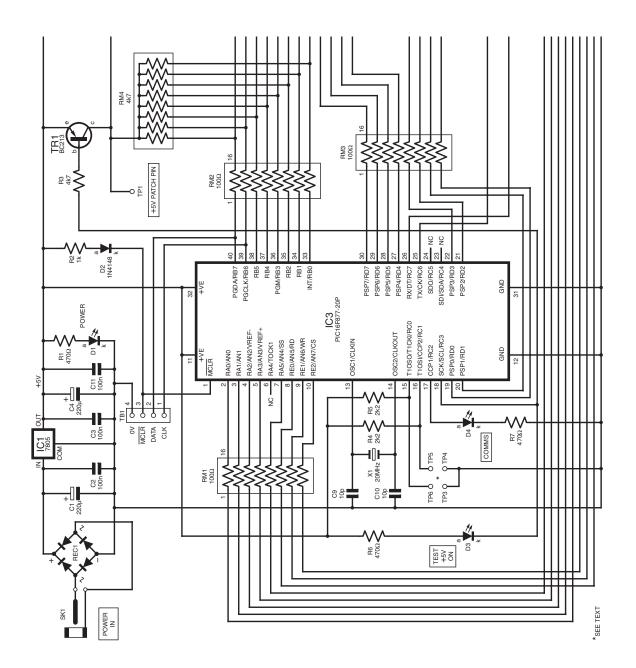

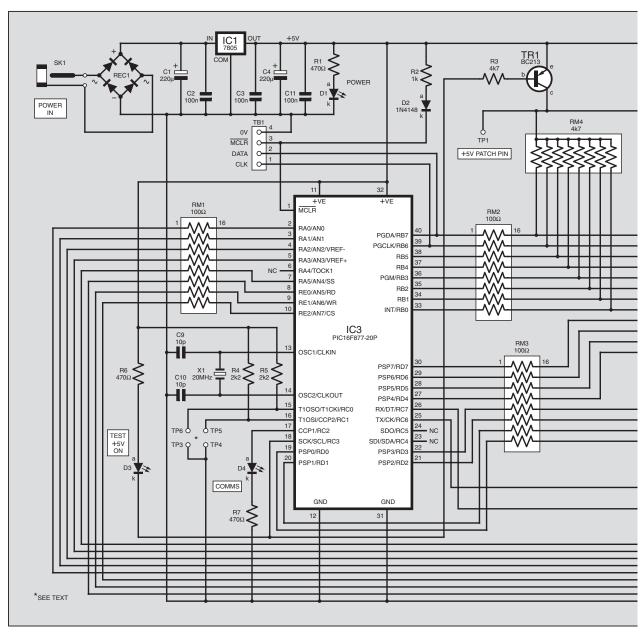

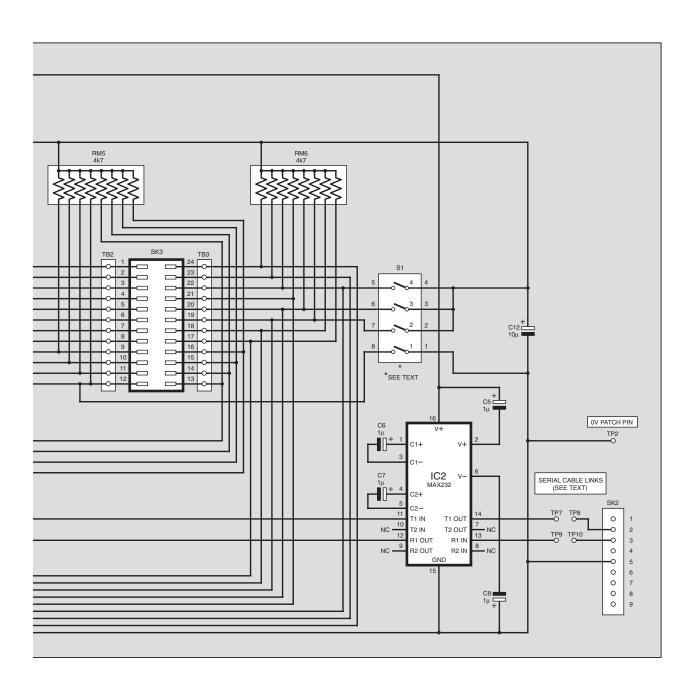

The complete circuit diagram for the Digital I.C. Tester is shown in Fig.1. When power is supplied to the board, it first passes through bridge rectifier REC1. If the input supply input is a.c., REC1 converts it to d.c. If the input is already d.c. it ensures that the polarity is correct for IC1, which then regulates the voltage down to approximately 5V. Capacitors C1 to C4 plus C11 provide smoothing.

A PIC16F877-20 microcontroller, designated as IC3, is used as the core of the circuit and is run at its maximum speed of 20MHz, as defined by crystal X1. Since this design uses RS232 protocol to interface to a serial port on a PC, a voltage level converter is employed to convert the PIC's 5V logic levels to the ±12V levels required by the RS232 standard (many PCs do not actually require this higher voltage for serial comms input and will accept +5V/0V inputs. Ed).

This is accomplished by IC2, a MAX232 line driver. Capacitors C5 to C8

are used by IC2's internal circuitry to convert the supplied voltage from 5V to ±12V. Connection to the PC is via a 9-pin female D-type connector, SK2.

To test the functionality of a digital logic i.c., a known set of logic levels must be presented on each pin and the resulting responses received back from the i.c. then analysed.

#### I/O PINS

The PIC16F877 has a total of 33 I/O (input/output) pins. Of these, 24 are used to connect the PIC to the i.c. under test. Each of the 24 I/O pins is connected to a pin on the i.c. test socket (SK3) via a  $100\Omega$  resistor, within resistor modules RM1 to RM3. These resistors act as current limiters to protect the PIC and the device under test. The danger is that an output of the test i.c. could become connected to a PIC I/O pin also designated as an output.

Each pin on the i.c. test socket is biassed to the +5V test power rail via a  $4k7\Omega$  resistor (within resistor modules RM4 to RM6). This is to force unused pins on the test socket to a known logic level, and also enables open collector TTL i.c.s that have their outputs either floating or pulled to ground to be tested.

During the test cycle, the PIC sends a low logic level to the base of transistor

Fig.1. Complete circuit diagram for the Digital I.C. Tester.

TR1 via resistor R3, which in turn applies power to the i.c. under test, via either the power patch pin (TP1) or via the dual-inline (d.i.l.) switch module S1.

Transistor TR1 also supplies +5V to the common pins of the pull-up resistors within modules RM4 to RM6. As soon as testing is complete, TR1 is switched off automatically, disconnecting power from the test i.c. Capacitor C12 provides smoothing of the switched +5V rail from TR1.

With power applied to the board and TR1 off (non-test mode), the PIC's RB6 and RB7 pins are available to allow an external programmer access to the PIC.

#### **POWER SUPPLY**

It is expected that when in service the project will be powered from a sealed plug-in mains power supply adaptor. Either an a.c. or d.c. power supply unit can be used and the connections to the printed circuit board (p.c.b.) are not polarity sensitive.

A power supply unit capable of supplying around 100mA and between 9V to 12V should be ideal. If the input voltage exceeds this, then it might be necessary to fit a larger heatsink to IC1. The prototype draws approximately 30mA when in standby, rising when testing. The exact current drawn will depend on the i.c. being tested.

#### TEST SOCKET

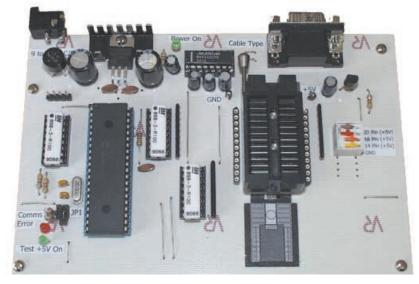

There are several possible choices for the method that will be used to connect i.c.s to the tester via socket SK3. The preferred method is a ZIF (Zero Insertion Force) socket. They are available in different sizes and formats but one should be chosen that accepts i.c.s of up to 24 pins and different package widths (a "universal" type).

The ZIF socket can be mounted directly on the board, or a 24-pin turned socket can be fitted first and then the ZIF pushed firmly into that. This allows the ZIF to be easily removed and used elsewhere if required. If a turned pin socket is not available, two rows of turned pin socket strips can be used instead.

Provision has been made on the p.c.b. to accommodate two pairs of turned pin socket strips, one pair of 10 pins (within the SK3 area), and one pair of 12 pins (TB2 and TB3) which may be used if it is decided not to use a ZIF socket. This allows narrow i.c. packages of up to 20 pins or the wider packages of up to 24 pins to be tested. Though not as convenient as a ZIF, this does make a cheaper option.

#### D.I.L. SWITCH OPTIONS

Power can be applied to the i.c. under test either via the jumper patch pins (TP1 and TP2), or predefined power configurations can be selected from the 4-way d.i.l. switch bank, S1. This switch allows a GND (0V) connection to be made to pin 12 of the test socket and a +5V connection to be made to pins 19, 20 and 22, as

### **COMPONENTS**

Resistors

$\begin{array}{cccc} \text{R1, R6, R7} & 470\Omega \text{ (3 off)} \\ \text{R2} & 1\text{k} \\ \text{R3} & 4\text{k7} \\ \text{R4, R5} & 2\text{k2 (2 off)} \\ \text{RM1 to} \end{array}$

RM1 to RM3 100Ω 8 x

individual resistors d.i.l. module (3 off)

RM4 to RM6 4k7 8 x commoned resistors s.i.l. module

(3 off) All 0.25W 5% carbon film or better except RM1 to RM6.

Capacitors

C1, C4 220*u* radial elect. 25V (2 off)

C2, C3, C11 100n ceramic disc,

5mm pitch (3 off)

C5 to C8  $1\mu$  radial elect. 50V (4 off) C9, C10 10p ceramic disc, 5mm

pitch (2 off) C12 10μ radial elect. 16V

Semiconductors

REC1 D1, D3 bridge rectifier 50V 1A green l.e.d., 3mm (2 off) 1N4148 signal diode D2 D4 red I.e.d., 3mm TR1 BC213 pnp transistor (or similar) IC1 7805 +5V 1A voltage regulator IC2 MAX232 RS232 line driver IC3

PIC16F877-20P microcontroller, preprogrammed (see text)

Miscellaneous

X1 20MHz crystal S1 4-way s.p.s.t. d.i.l. switch, p.c.b. mounting (see text) SK1 power connector (see text)

SK2 9-way D-type sub-min.

connector, female, p.c.b. mounting

SK3 24-pin universal ZIF socket (see text)

TB1 4-way terminal pin

TB2, TB3 turned pin socket strip (2 x 12-way) (see text)

Printed circuit board, available from the *EPE PCB Service*, code 371; p.c.b. supports (4 off); 40-pin d.i.l. socket; 16-pin d.i.l. socket (4 off); heatsink 21°C/W for IC1 and mounting hardware; solid insulated wire for jumper links; solder, etc.

Approx. Cost Guidance Only

Only excl. connectors

### **DIGITAL I.C. TESTER CIRCUIT BOARD**

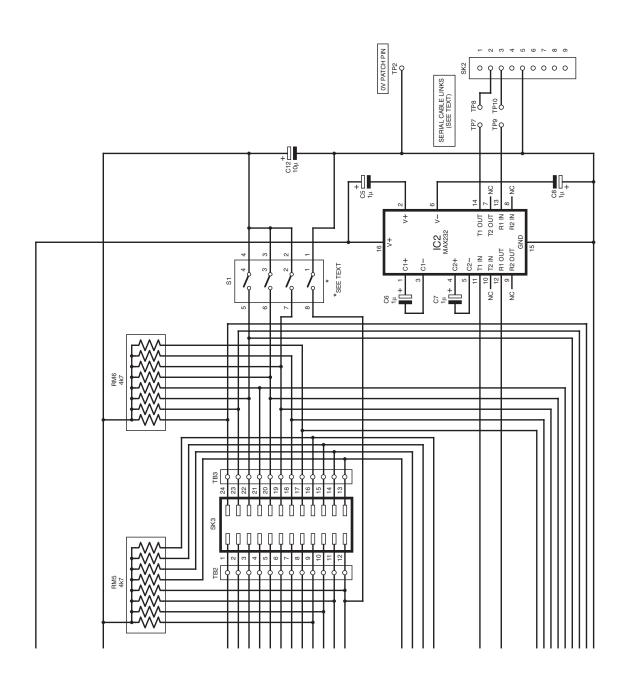

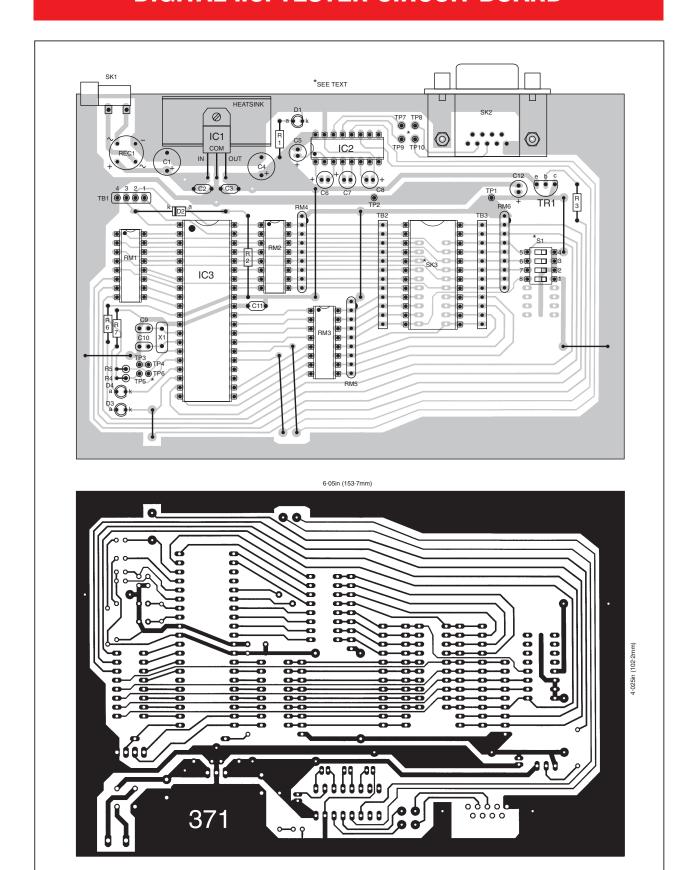

Fig.2. Printed circuit board component layout and full size copper foil master track pattern.

required. These combinations cater for the majority of 14, 16 and 20-pin packages.

Provision has been made on the p.c.b. to accommodate an 8-way d.i.l. switch bank for S1 if required instead of the 4-way (using the unused holes seen below S1 on the p.c.b. in Fig.2). The additional four ways can be hard-wired to any combinations wanted. The p.c.b. tracks located below the switch should make the setting up of these combinations easy.

#### **CONSTRUCTION**

The Digital I.C. Tester is constructed on a single-sided p.c.b. whose component layout and tracking details are shown in Fig.2. This board is available from the *EPE PCB Service*, code 371.

It is recommended that good quality i.e. sockets are used for IC2, IC3 and the three  $100\Omega$  resistor modules, RM1 to RM3. Assemble the board in any order you prefer, but preferably making the link-wire connections first

fer, but preferably making the link-wire connections first.

No provision for a power socket was

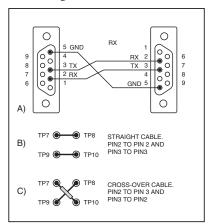

The two link wires located to the left of SK2, the 9-pin RS232 connector (between TP7/TP8 and TP9/TP10), help determine which type of serial cable will be used, see Fig.3. If a straight-through serial cable is to be used, pin 2 to pin 2, pin 3 to pin 3, then these links should be parallel to each other as shown in Fig.3b.

If a cross-over serial cable is being used (pin 2 to pin 3 and pin 3 to pin 2 – as in Fig.3a) then the links should be crossed as in Fig.3c. Place a small piece of sleeving over one of the link wires so that they do not short together.

Fig.3. Links to be made in respect of serial lead type, see text.

No provision for a power socket was made on the p.c.b. due to the different types of power connectors currently in use. Instead, two terminal pins can be fitted and then an appropriate power socket for the chosen power supply soldered directly to these, as in the prototype.

Be careful to observe the correct polari-

ty of the semiconductors, electrolytic

capacitors and l.e.d.s. It is also worthwhile

orientating the i.c. sockets as shown, even

though they are not actually "polarity con-

scious" in the normal sense. Doing so helps

to ensure that the i.c.s. themselves are

the tester to the PC, until preliminary

Do not insert IC2 and IC3, or connect

If the board is to be used as is (i.e. with-

out a case), attaching small stick-on rubber

feet to each corner is a wise precaution. If

the intention is to house it in a suitable

case, a 24-pin wire-wrap type socket can

be used for SK3 as this will provide ade-

quate clearance between the components

on the p.c.b. and the case lid. The ZIF sock-

et can then be plugged into the wire-wrap

socket. A similar arrangement can be used

inserted the correct way round.

checks have been completed.

for mounting d.i.l. switch S1.

Note that there are three holes located around IC1 that are not used. These points enable power to be tapped off for use with other circuits if desired.

There are four terminal pins (TP3 to TP6) located to the left of IC3. Ignore pins TP3 and TP5. The TP4/TP6 pair control the RS232 interface rate. With the default PIC firmware and 20MHz crystal, connecting TP4 to TP6 selects an interface speed of 57-6K baud. Without this link, 19-2K baud is used. A plug-in jumper link was used on the prototype.

#### FIRST TESTS

Once construction is completed, recheck that all components have been oriented correctly and look for any solder splashes or bridges that might have occurred during assembly. Using a multimeter set to ohms, check the resistance across capacitor C4 to ensure that there is no short circuit. A brief reading may be obtained whilst C3 and C4 charge.

If all is OK, continue testing, otherwise do not attempt to apply power until the problem has been removed as IC1, the bridge rectifier or the power supply unit could be damaged.

Making sure that the board is not resting on anything conductive, connect a suitable power supply. Switch on the power and l.e.d. D1 should illuminate. Switching the multimeter to d.c. volts, measure the voltage on pins 11 (+VE) and 31 (GND) of the socket for IC3. A reading of approximately 5V, within a few percent, should be seen.

If the 5V rail is not present or l.e.d. D1 does not illuminate, carefully check around IC1 and IC3 for short circuits or dry joints, and check the polarity of the D1.

Switch off the power supply and disconnect it from the mains supply when making any changes to the board.

### ASSEMBLY COMPLETION

Once everything seems to be in order, insert IC2 and IC3, being careful of correct orientation and not to let any of the i.c. pins bend under whilst being inserted. The PIC, IC3, can either be a preprogrammed version (see later) or if a suitable in-circuit programmer is available (*Toolkit Mk3/TK3* for instance), it can be programmed on board via the TB1 connector.

Referring to Fig.1, resistor R2 and diode D2 permit the correct use of the PIC's MCLR pin 1 both during and after programming.

The completed unit needs to be connected to a suitable serial port on the PC. The cable should have a 9-pin male connector on one end for the unit and a suitable connector for the PC's serial port on the other. Fig.3a shows a cable schematic for a computer having a 9-pin serial port connector. For this cable, the cable selector links on the p.c.b. should be straight, as in Fig.3b (see earlier).

#### INSTALLING PC SOFTWARE

The PC software has been written in Visual Basic 6 (VB6) and should run on any recent Microsoft operating system including Windows 95, 98, ME, NT 4.0, 2000 and XP.

The installation set consists of four files: **Setup.exe**, which is the installation program, **Setup.lst**, which provides setup control parameters to the **Setup.exe**, plus **ICTest1.cab** and **ICTest2.cab** which contain the actual Digital I.C. Tester program, VB6 runtime files and i.c. model definition (type number) files.

Create a temporary new folder having any name of your choice, e.g. C:\ICTester, and copy the files into it. Then run the Setup.exe either by entering C:\ICTester\Setup.exe in the Windows run dialogue window or by double-clicking on Setup.exe in the File Explorer.

Once the setup has begun, most users should be able to accept the default settings offered. During the installation process, you may be asked to restart your computer if you have not previously installed the Visual Basic 6 runtime components or they are out of date. Reboot the computer and restart the setup process as required.

The temporary directory **C:\ICTester** can be deleted if no longer required once the setup is complete. If running the installation from the *EPE* CD-ROM, insert the disk into the disk drive and run the **Setup.exe** program located on it, as described above, then follow the prompts.

Once complete, the Setup program will create a new program group called **Digital I.C. Tester**. You can find it be clicking the

Start icon on the lower left hand side of the main Windows screen, and then selecting programs. You should see it listed there.

### TESTING THE INTERFACE

Connect the serial cable and power supply unit and switch on. The l.e.d. D1 should illuminate. Also, to confirm that the PIC is running and executing its firmware, l.e.d. D4 should also illuminate.

Start the PC program running and you will be presented with the main working area, similar to Photo 1.

Photo 1. Main working area toolbar on PC screen.

By default, the PIC firmware and the PC software are set to communicate at 19·2K baud (TP4/TP6 link excluded – see earlier).

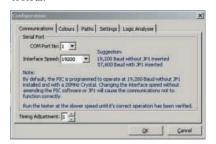

The PC software must be configured to use the COM port that you have connected the serial cable to. By default, the software uses COM:1. If you are not using COM:1, you can change this setting by selecting the Tools menu and then Configuration, which produces a display such as in Photo 2. A short-cut is to click the spanner icon on the toolbar.

Photo 2. Serial communications configuration screen.

From here, you can change settings that control communication, default display colours, directories or folder locations and some other *ad-hoc* settings. Change the COM port to the required setting and click OK. All configuration changes are stored for later use.

Next you need to test the actual communication link between the PC and the Digital I.C. Tester. Again, select Tools from the top and this time select Confirm Communication Interface at the bottom of the menu.

A screen will be displayed detailing some checks you should first make. When you are ready, click the Start button. You will see some text scroll up in the panel on the right hand side of the window and perhaps l.e.d. D4 flickering on the tester.

The panel on the window will turn green if the communications link is satisfactory. If it turns red this indicates that the computer cannot establish a communications link with the tester. Perform the checks as detailed and try again. Most often the communications failure is due to the wrong COM port being selected or an incorrect cable being used.

If all is well, you can now proceed to test an i.c., but note that if l.e.d. D4 illuminates constantly during the testing process, this indicates a possible communications problem. In which case check the serial cable and the PC software speed settings in the configuration window.

#### **TESTING AN I.C.**

The software is supplied with profiles for a selection of common TTL and CMOS devices. For the following testing example we shall use a TTL 74LS00, a quad 2-input NAND gate. To properly follow this discussion now, it is best to have the PC software running.

Drop the i.c. to be tested into the test socket, making sure that the bottom right hand pin of the i.c. is located in the bottom right hand pin of the socket.

Different i.c.s can have their power rail pins located in different positions. Typically, the bottom left hand pin is GND and the top right hand pin is +VE but this is by no means always the case. The rows of turned pin sockets alongside the test socket can be used to route power to the correct pins, but more on this in a moment.

Next, you need to tell the PC software which i.c. type is going to be tested. To do this, you need to load a profile file that relates to the specified type. This file contains details about the number of pins on the i.c., which pins are inputs and outputs, have no internal connection and which are its power pins.

The profile also contains detailed instructions on how to test the i.c. From the program's main menu select File and then Load IC Profile. After a few moments, a list of the available profiles should be displayed in the right hand panel (see Photo 3).

If the panel is empty then you will need to tell the software where the "Datasheets" folder is located. The default is **c:\Program Files\ICTester\DataSheets**. The left hand panel allows you to browse your computer's drives and folders until you locate the "Datasheets" folder.

Photo 3. Selection screen for i.c. types.

Scroll down the list of available profiles and select "7400". You can double-click to load or click once and then click the Load button. The Profile Directory window should now disappear and you will see just the main application window. On the status bar at the bottom, though, you should now see some additional information, such as that in Photo 4.

Quad 2 Input NAND, Model Loaded. 7400 COM:1 @19200 Baud

Photo 4. Status bar.

#### **TESTING OPTIONS**

To start the testing process, select IC Test from the top menu and then select Test Specified IC. A window similar to that in Photo 5 will be displayed.

Photo 5. The "testing" screen.

There are four main areas to this window. The Start and Stop buttons are used to begin and terminate the testing process accordingly. The Performance panel is used to get additional information displayed during the testing process.

If Update Pin Display has a check mark displayed, a representation of the i.c. being tested will be displayed on the screen. As the logic levels change on the actual device being tested, they will be reflected on this display (this is useful when the Single Step option is also selected).

The function Update Logic Trace will record a trace similar to a storage oscilloscope that can be studied after the testing process has been completed. Enabling the Real-time Plot option will keep the trace updated as the testing progresses instead of just displaying the results at the end of the test.

These options, if selected, will impact on the performance of slower PCs. To get the best possible speed, do not enable these options. However, for now, enable all three so you can see exactly what happens.

The Test Mode panel controls how the testing is performed. Normally, Single Test would be selected. If you suspect that a device has an intermittent problem, though, you can set the software to do a Continuous Test. The test-cycle will then be repeated up to 999 times.

Abort On Error will terminate the testing cycle if any error is detected in the i.c.

Single Step is useful if, for example, you want to probe around the i.c. under test

Photo 6. Pin connections dialogue screen.

with an oscilloscope or logic probe. Every time a pattern is sent to the test i.c., the PC software will display a message box asking you to press the <CR> (<ENTER>) key before it moves onto the next step.

The Test Statistics panel shows how many test cycles have been made (0 to 999), the current sequence or pattern number being executed as specified in the device profile file, and how many test-cycles the device has passed or failed.

#### TEST PROCEDURE

When ready, click the Start button. Because this is the first time you have tested an i.c. with this power pin configuration, a dialogue box is displayed (see Photo 6). The picture shows how to correctly apply power to the i.c. under test. Also, it shows you how the i.c. should be inserted in the socket.

Notice that in this case, no power patch wires are required as this i.c. package is supported by the on-board d.i.l. switches. So, set d.i.l. switches S1/3 and S1/4 to the ON position, as indicated.

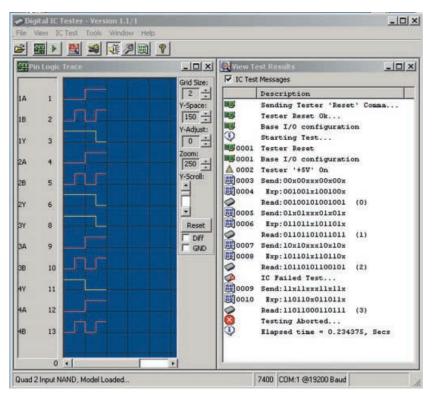

Press OK to start the test. All being well, after a couple of seconds you should have a display similar to that in Photo 7.

Select Window from the top menu and then Tile Vertically to get the software to arrange everything neatly for you on the screen.

In the case of the i.c. represented in Photo 7, it actually failed during the testing process. The right hand panel shows that the problem occurred with pattern sequences 0007 and 0008. Sequence 0007 shows what the Digital IC Tester sent to the i.c. Sequence 0008 shows what the device profile says should be the response from the i.c. The next line shows what the response from the i.c. actually is. An "X" means Don't Care about the logic level.

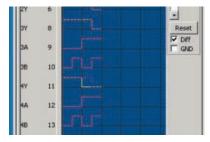

Whilst this is helpful, it is not too clear exactly what the problem is. The trace on the left hand side of the screen shows the logic levels present on each pin of the i.c. during the test. The trace is updated after each Read operation is performed.

The display has four yellow traces which are the outputs of each of the four NAND gates. Since they should all behave the same, it's quite clear that there is a problem with the gate whose output is on pin 11. In some cases, though, the actual problem might not be clear, especially if the i.c. only contains one or two gate arrays. If you select Diff on the Pin Logic Trace, the trace display will change and look similar to that in Photo 8.

The dotted line indicates what the profile is expecting back as a response from the i.c. under test. As can be seen with pin

Photo 8. Test screen in "difference" highlighting mode.

Photo 7. Typical screen display during testing, on this occasion showing that the i.c. is faulty (see text).

11, the logic level dropped from high to low before it was expected. Another option available is GND, located directly under the Diff option. Enabling GND forces a dotted line showing where the low logic level for each pin would be on the display. This makes a useful trace separator when the screen starts looking crowded.

#### **CREATING PROFILES**

Since the number of i.c. devices on the market is constantly changing, the tester would soon become obsolete if the user did not have the ability to add new profiles as required. To create a new profile, select Create IC Profile on the main Tools menu, see Photo 9.

You will need to enter the i.c.'s type number and a brief description about the device. Next select how many pins the device has, and specify which pins are designated as inputs, outputs, power or have no internal connection. You do this by

Photo 9. Creating an i.c. pin function profile.

Photo 10. Creating an i.c. test procedure profile.

repeatedly clicking on each pin in the usage column. Additionally, you can create short tags (descriptions) for each pin, which are displayed along with the pin numbers on the Logic Trace screen. When ready, click the Next button.

#### TEST EXAMPLE

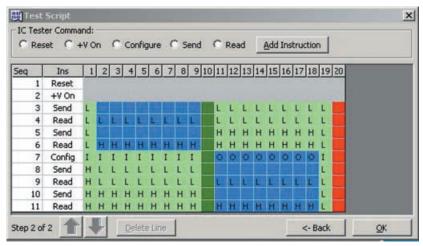

You must now tell the Tester what logic levels to send to the i.c. and what the expected results will be (see Photo 10).

To test a 7400 quad 2-input NAND gate, for example, 10 instructions are required:

Sequence 1 – Reset. This sends a Reset command to the PIC and should always be included unless there is a specific reason not to. You can include as many Reset commands as required and at any location within the script.

Sequence 2 – +VE On. This switches on the +5V supply to the i.c. under test. It also applies +5V via transistor TR1 to the three commons of the pull-up s.i.l. resistor modules, RM4 to RM6.

**Sequence 3 – Send.** Here, we are sending low logic levels to pins 1, 2, 4, 5, 9, 10, 12 and 13. These pins were defined on the previous screen as inputs. You can only send logic levels to pins defined as inputs.

Photo 11. Example of a profile screen being set for multiple function pins.

Sequence 4 – Read. We now read back the logic levels from the i.c. being tested. We expect pins 1, 2, 4, 5, 9, 10, 12 and 13 to be low since we have set them low in the previous instruction. However, we must now indicate which logic levels are expected on each output pin. According to the truth table we looked at for a NAND gate earlier, all gates should return a high logic level. We now continue sending logic levels to the i.c. being tested and then reading back the actual logic levels from it.

There is no need to send a Config command in the above sequence since the PC software sends the required configuration based on the profile information you specified on the first screen during the profile creation.

#### **MULTIPLEXED PINS**

Some i.c.s, however, have pins that can be either an input or an output, depending on the logic level of some other pins, and the 74245 is an example of this (see Photo 11).

At Sequence 7, a Config command has been inserted. This enables the tester to be reconfigured and specify which pins are inputs or outputs. Testing resumes from Sequence 8.

Select the Reset command and click Add Instruction. A new line will be added to the display. Do the same for +VE On. Next, insert a Send command. This is the binary pattern we want to present to the i.c. under test. Logic levels are changed by clicking the cell on the new line that you want to change.

Normally, after a Send command, you will perform a Read. But this is not always the case. For the Read, you can specify that a pin designated as an output should have either a High or Low logic level or that it doesn't matter ("X").

Once the required instructions have been created, press OK to save the profile.

The up and down arrow buttons allow lines to be moved up and down in the execution order. The Delete Line button allows instruction lines to be removed from the profile.

## CONFIGURATION OPTIONS

The configuration options can be selected from the main menu and are located

under Tools, Configuration (see Photo 2 earlier). When selected, there are five groups of configuration settings that can be changed.

The first group deals with the serial interface characteristics. The COM port and interface speed are changed here. At the bottom of the screen there is a Timing Adjustment button. In certain circumstances, it is possible to under-run the PC's serial buffer. Increasing this value forces the PC software to wait longer for incoming data, the drawback being that the software will run slightly slower.

To check that this setting is correct, insert a known good i.c. into the tester and set for continuous testing. If after the default 999 tests no failures have been reported then the setting is correct. If any failures are detected then this value should be increased by a value of 1 and the test performed again.

The next group allows the information display colours to be changed. Clicking any of the coloured panels brings up the colour picker dialogue.

The Paths groups allows the default location of the Data Models (i.c. types) storage path to be specified. Clicking the ellipsis button on the right (the one with . . .) allows you to explore the available disk drives and folders and locate the location of the data model files.

The settings groups allow some display options and the DIP switch type and usage to be specified. The Show Tool Bar and Show Status Bar options allow the Tool and Status bars to be shown or hidden, which is useful if screen real estate is scarce.

In some cases, the software attempts to gain the user's attention by flashing messages on the screen. The option Allow Flashing Text controls whether these messages flash or are static.

The option Always Warn About Test IC Power Pin Configuration controls how the software warns the operator about the power pin configuration of the i.c. under test. If On, the software always issues a warning. If Off, the software only issues a warning when either the first i.c. of the session is to be tested or a new i.c. type has been selected that has a different power configuration from the previous type tested.

The DIP Type options control the look of the graphic used for showing the d.i.l.

switch settings. Select the type that best matches your d.i.l. switch type. The switch bank size defaults to 4-Way. If this is changed to 8-Way, indicating that you have opted to fit the 8-way switch for S1, the Setup DIPS ("DIPS" referring to the other name, dual-in-line-package, by which d.i.l. switches are sometimes known) button will be enabled.

Selecting Setup DIPS allows you to specify how you have wired the additional four switches.

The printer icon allows a template to be printed that contains all the texts required to label the Digital I.C. Tester. Also, a custom legend is printed that can be affixed next to the d.i.l. switch S1.

All configuration options are saved and automatically used the next time the PC software is started.

Photo 12. Logic analyser experimental screen.

It is worth noting that, in most cases, holding the mouse pointer over a control or button will provide some additional information on its use.

# EXTERNAL LOGIC ANALYSING

An additional feature was added to the software to experiment with displaying logic states for i.c.s running in-circuit on other p.c.b.s, and this has been left in the published software for reader's own experimentation purposes (see Photo 12).

A test connector, consisting of an i.c. test clip, connected to a piece of ribbon cable and terminated with a 24-pin i.c. header plug, allows the Digital I.C. Tester to be connected to the in-circuit i.c. Once connected the Logic Analyser function can be selected from the Tools menu.

The Logic Analyser monitors and reports the logic levels on between 1 and

24 pins. The pins to be monitored are selected in the Monitor Pins panel. An optional trigger pattern can be specified if required. A "tick" indicates a high logic state and the absence of a tick indicates a low logic state. When all monitored pins have the specified trigger pattern, the Analyser is triggered.

There are two primary modes of operation for the Analyser. The mode Only Detect Pattern Changes displays each new logic pattern as it changes. Free Running grabs the logic levels as fast as possible. If Free Running is selected, an optional delay can be specified from 0 to 9999ms between each sample being made. Update Pin Display and Logic Display work as previously discussed. The Activate Device Pull-Ups controls whether the s.i.l. pull-up resistor modules (RM4 to RM6) have their common connections powered or not.

When the logic analyser starts, it instructs the PIC to "grab" logic level status information as fast as possible and transmit this to the PC. The PC then attempts to process and display this information. Because of this, the analyser has several practical limitations.

Firstly, due to the hardware design and

the way the PIC operates internally, the PIC's I/O ports are read at slightly different times. This means that when changing logic levels are trying to be captured, there is a possibility of inconsistent or unexpected results being displayed.

Also, no matter what settings you select, the PIC frantically transfers data as fast as it can to the PC and does not store any of the results internally. This means that the capture speed is limited to the maximum speed of the serial interface, making it quite slow in relation to today's computer speeds.

#### **CONCLUSION**

The Digital I.C. Tester has successfully tested a variety of i.c.s without any problem, including 74, 74F, 74LS, 74HC and CMOS 4000 series. The only slight exception to this was with the HC series. These refused to test correctly with the original prototype which used 330 $\Omega$  buffer resistor modules (RM1 to RM3). These were swapped for  $100\Omega$  ones, as specified for this published version, and then the offending i.c.s tested fine.

The design aims to give a go/no-go logic report on the i.c. being tested. It is beyond

the scope of the tester to attempt to measure the i.c.'s analogue operational parameters and compare them with its technical specification. Perhaps when a PIC is available with 24 onboard analogue-to-digital converters, the author will revisit the design.

#### **ACKNOWLEDGEMENT**

The author would like to thank his brother Peter for supplying a large selection of "test subjects", most of which looked like they belong in the Science Museum!

#### **RESOURCES**

All software for this project is available for free download from the *EPE* ftp site, or on CD-ROM (for which a charge applies) from the *EPE* Editorial office, see the *EPE PCB Service* page for details. The PIC program software is supplied in MPASM format (.ASM and .HEX). See this month's *Shoptalk* page for details of obtaining preprogrammed PICs.

The datasheet for the MAX232 is available from the Maxim website at www.maxim-ic.com.

Datasheets for the majority of TTL i.c.s can be found on Texas Instruments web site at **www.ti.com**.